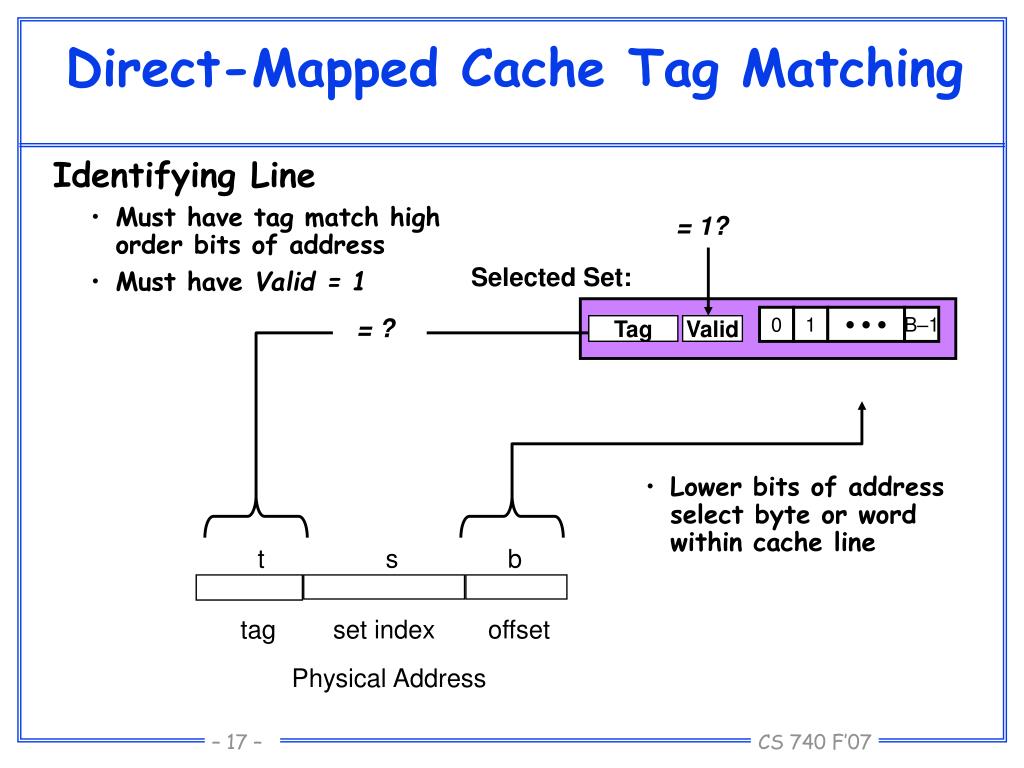

To confuse matters, Intel uses cache line to indicate the smaller unit that shares a tag with other lines in a sector while some others use cache block/line for the larger unit with the term sector used for the portion that can be individually invalidated.įor the level of complexity for this type of exercise, one can reasonably assume that sectoring is not used, so a tag match would indicate a hit regardless of the offset. Accessing Direct-Mapped Caches Line matching and word selection Line matching: Find a valid line in the selected set with a matching tag Word selection: Then extract the word 1 t bits s bits 0110 i 100 m-1 0 b bits tag set indexblock offset selected set (i): (3) If (1) and (2), then cache hit, and block offset selects starting byte. The block-offset-bits need to be enough bits to index each byte in a cache-line (block).

Sectoring can also be used to directly fill the cache and allow early restart alternatives include using a side (fill) buffer with extra valid bits (similar to a write buffer) and waiting for the entire cache block is loaded before restarting execution. This could be used to avoid unnecessary writebacks, e.g.)

#DIRECT MAPPED CACHE TAG INDEX OFFSET FULL#

(It would also be possible to include fully independent coherence state, e.g., MESI, rather than just validity. Use random or LRU replacement policy when cache full Memory address breakdown (on request) Tag field is unique identifier (which block is currently in slot) Offset field indexes into block (by bytes) Each cache slot holds block data, tag, valid bit, and dirty bit (dirty bit is only for write-back) The whole cache maintains LRU. For an inclusive cache, this avoids unnecessary back-invalidation of L1 cache. In theory a valid bit could be provided for every smallest unit of access (commonly an 8-bit byte), but sectoring is more commonly used to allow an outer level of cache to use a larger block size than L1 caches without forcing all the data associated with a tag to be invalidated when the smaller unit needs to be. With sectoring a cache block can have multiple valid bits, in which case the tag might match but the valid bit for the section corresponding to the offset might be cleared (indicating that the section is invalid). If the cache blocks are not sectored, then if the tag field matches any offset within the block will be a hit.

0 kommentar(er)

0 kommentar(er)